# M5W1793-02P

### FLOPPY DISK FORMATTER/CONTROLLER

#### 1. DESCRIPTION

The M5W1793-02P is a floppy disk formatter/controller device which accommodates single and double density formats

The device is designed for use with microprocessors or microcomputers.

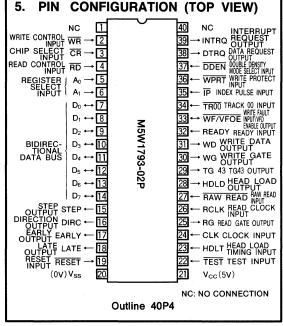

The device is fabricated with the N-channel silicon gate ED-MOS technology and is packaged in a 40-pin DIL package.

### 2. FEATURES

- Single 5V supply voltage

- Accommodate single and double density formats IBM 3740 single density format

IBM system 34 double density format

- Selectable sector length (128, 256, 512 or 1024 bytes/ sector)

- Side select compare

- Single/multiple sector read or write with automatic sector search

- Selectable track to track stepping time

- Write precompensation

- DMA or programmed data transfers

- Window extension

### 3. APPLICATIONS

- Single or double density floppy disk drive formatter/controller

- 8-inch or mini floppy disk interface

#### 4. FUNCTION

The M5W1793-02P is a floppy disk formatter/controller that can be used with most microprocessor or microcomputer

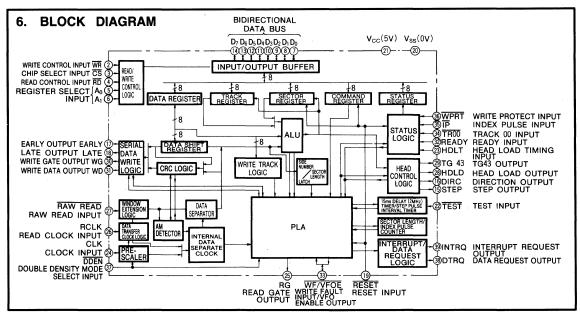

systems. The hardware of the M5W1793-02P consists of a floppy disk interface, a CPU interface and a PLA control logic. The total chip can be programmed by eleven 8-bit commands. The floppy disk interface portion performs the communication with the floppy disk drive under control of the PLA control logic. The CPU interface portion has five registers — command, data, status, track and sector register — and communicates with the CPU through the data bus. These functions are also controlled by the PLA.

# M5W1793-02P

FLOPPY DISK FORMATTER/CONTROLLER

# 7. PIN DESCRIPTION

| Pin                             | Name                   | Input or output | Functions                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|---------------------------------|------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NC                              | No internal connection |                 | NC(pin 1) is not internally connected                                                                                                                                                                                                                                                                                                                          |  |  |  |

| WR                              | Write control input    | Input           | Write signal from a master CPU (Active low).                                                                                                                                                                                                                                                                                                                   |  |  |  |

| CS                              | Chip select input      | Input           | Chip select (Active low).                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| RD                              | Read control input     | Input           | Read signal from a master CPU (Active low).                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                 |                        |                 | Register select inputs. These inputs select the register under the control of the $\overline{\text{RD}}$ and $\overline{\text{WR}}$ .                                                                                                                                                                                                                          |  |  |  |

|                                 | ,                      |                 | A <sub>1</sub> A <sub>0</sub> RD WR                                                                                                                                                                                                                                                                                                                            |  |  |  |

| A <sub>0</sub> , A <sub>1</sub> | Register select input  | Input           | 0 0 STATUS REGISTER COMMAND REGISTER 0 1 TRACK REGISTER TRACK REGISTER 1 0 SECTOR REGISTER SECTOR REGISTER 1 1 DATA REGISTER DATA REGISTER                                                                                                                                                                                                                     |  |  |  |

| D <sub>0</sub> ~D <sub>7</sub>  | Bidirectional data bus | In/Out          | Three-state, non-inverted bidirectional data bus.                                                                                                                                                                                                                                                                                                              |  |  |  |

| STEP                            | Step output            | Output          | Step pulse output (Active high).                                                                                                                                                                                                                                                                                                                               |  |  |  |

| DIRC                            | Direction output       | Output          | Direction output. High level means the head is stepping in and low level means the head is stepping out.                                                                                                                                                                                                                                                       |  |  |  |

| EARLY                           | Early output           | Output          | This signal is used for write precompensation. It indicates that the write data pulse should be shifted earty.                                                                                                                                                                                                                                                 |  |  |  |

| LATE                            | Late output            | Output          | This signal is also used for write precompensation. It indicates that the write data pulse should be shifted late.                                                                                                                                                                                                                                             |  |  |  |

| RESET                           | Reset input            | Input           | Reset input (Active low). The device is reset by this signal and automatically loads "03" (hexadecimal) into the command register. The not-ready-status bit is also reset by this signal. When reset input is made to be high, the device executes restore command even unless READY is active and the device loads "01" (hexadecimal) to the sector register. |  |  |  |

| TEST                            | Test input             | Input           | This input is only used for test purposes, so user must tie it to V <sub>CC</sub> or leave it open unless using voice coll actuated motors.                                                                                                                                                                                                                    |  |  |  |

| HDLT                            | Head load timing input | Input           | When the device finds high level on this input, the device assumes that the head is engaged on the media. Active high.                                                                                                                                                                                                                                         |  |  |  |

| CLK                             | Clock input            | Input           | Clock input to generate internal timing. 2MHz for 8-inch drives, 1MHz for mini drives.                                                                                                                                                                                                                                                                         |  |  |  |

| RG                              | Read gate output       | Output          | This signal shows the external data separator that the syncfield is detected.                                                                                                                                                                                                                                                                                  |  |  |  |

| RCLK                            | Read clock input       | Input           | This signal is internally used for the data window. Phasing relation to raw read data is specified but polarity (RCLK high or low) is not important.                                                                                                                                                                                                           |  |  |  |

| RAW<br>READ                     | Raw read input         | Input           | This input signal from the drive shall be low for each recorded flux transition.                                                                                                                                                                                                                                                                               |  |  |  |

| HDLD                            | Head load output       | Output          | This output signal controls the loading of the head of the drive. The head must be loaded on the media by this high-level output.                                                                                                                                                                                                                              |  |  |  |

# FLOPPY DISK FORMATTER/CONTROLLER

| Pin     | Name                                       | Input or output | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TG43    | TG 43 output                               | Output          | This output is valid only during disk read/write operation and it shows the position of the head. High level on this output indicates that head is positioned between track 44 to 75.                                                                                                                                                                                                                                                                                            |

| wg      | Write gate output                          | Output          | This signal becomes active before disk write operations are to occur.                                                                                                                                                                                                                                                                                                                                                                                                            |

| WD      | Write data output                          | Output          | This signal consists of data bits and clock bits. It becomes active for every flux transition. Active high.                                                                                                                                                                                                                                                                                                                                                                      |

| READY   | Ready input                                | Input           | This signal shows the device the drive is ready. In the disk read/write operation except for TYPE 1 command operation, low level input terminates current operation and the device generates the INTRQ. In the TYPE 1 command operation, this signal is neglected. Not ready bit in the status register is the inverted form of this input.                                                                                                                                      |

| WF/VFOE | Write fault input/<br>VFO enable<br>output | In/Out          | This is a bidirectional signal. It becomes write fault input when WG is active. In the disk write operation, low level signal on this input terminates the write operation and makes INTRQ active. This signal also appears in the status register as the write fault bit. When WG is inactive, this signal works as VFO enable output. VFOE output is also an open drain type, so pull it up to V <sub>CC</sub> and never input active write fault signal write WG is inactive. |

| TR00    | Track 00 input                             | Input           | This signal indicates that the head is located on the track 00 to the device. Active low.                                                                                                                                                                                                                                                                                                                                                                                        |

| ĪP      | Index pulse input                          | Input           | This input indicates to the device that an index hole of the diskette has been encountered.                                                                                                                                                                                                                                                                                                                                                                                      |

| WPRT    | Write protect input                        | Input           | Low level signal on this input informs the device that the drive is in the write protected state. Before disk write operations, this signal is sampled and an active low signal will terminate the current command and set INTRQ. The write protect status bit in the status register is also set.                                                                                                                                                                               |

| DDEN    | Double density mode select input           | Input           | This input determines the device operation mode. When \$\overline{DDEN}=0\$, double density mode is selected. When \$\overline{DDEN}=1\$, single density mode is selected.                                                                                                                                                                                                                                                                                                       |

| DTRQ    | Data request output                        | Output          | DTRQ is an open drain output, so pull up to $V_{\rm CC}$ by the 10k resistor. In the disk read mode, DTRQ indicates that data is assembled in the data register. In the disk write mode, it indicates that the data register is empty. DTRQ is reset by the read data or write data operation.                                                                                                                                                                                   |

| INTRQ   | Interrupt request output                   | Output          | INTRQ is also a open drain output, so pull up to $V_{CC}$ by the 10k resistor. INTRQ becomes active at the completion of any command and is reset when the CPU reads the status or writes the command.                                                                                                                                                                                                                                                                           |

| NC      | No internal connection                     |                 | NC (pin 40) is not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# M5W1793-02P

# FLOPPY DISK FORMATTER/CONTROLLER

## 8. COMMAND DESCRIPTION

WR signal.

There are 11 different commands. By setting  $\overline{CS}$  to "0",  $A_0$  to "0" and  $A_1$  to "0", the commands are written into the M5W1793-02P from the data bus at the rising edge of the

The commands are classified into four Types : type 1, Type 2, Type 3 and Type 4.

Table 8.1 List of Commands

| Command type    | Command                 | MSB |   |   | C | ode            |                |                | LSB                   |

|-----------------|-------------------------|-----|---|---|---|----------------|----------------|----------------|-----------------------|

|                 | Restore command         | 0   | 0 | 0 | 0 | h              | V              | r <sub>1</sub> | r <sub>0</sub>        |

|                 | Seek command            | 0   | 0 | 0 | 1 | h              | ٧              | r <sub>1</sub> | r <sub>0</sub>        |

| Type 1 commands | Step command            | . 0 | 0 | 1 | u | h              | ٧              | r <sub>1</sub> | <b>r</b> <sub>0</sub> |

|                 | Step-in command         | 0   | 1 | 0 | u | h              | ٧              | r <sub>1</sub> | <b>r</b> <sub>0</sub> |

|                 | Step-out command        | 0   | 1 | 1 | u | h              | ٧              | r <sub>1</sub> | <b>r</b> <sub>0</sub> |

| <b>-</b> 0      | Read sector command     | 1   | 0 | 0 | m | S              | E              | С              | 0                     |

| Type 2 commands | Write sector command    | 1   | 0 | 1 | m | S              | Е              | С              | <b>a</b> <sub>0</sub> |

|                 | Read address command    | 1   | 1 | 0 | 0 | 0              | E              | 0              | 0                     |

| Type 3 commands | Read track command      | 1   | 1 | 1 | 0 | 0              | Е              | 0              | 0                     |

|                 | Write track command     | 1   | 1 | 1 | 1 | 0              | Е              | 0              | 0                     |

| Type 4 commands | Force interrupt command | 1   | 1 | 0 | 1 | l <sub>3</sub> | l <sub>2</sub> | I <sub>1</sub> | l <sub>0</sub>        |

Note 1: The M5W1793-02P features positive logic data bus and so the codes are written into the M5W1793-02P without modification.

Each command has a flag option. Refer to these options in Table. 8.2.

# FLOPPY DISK FORMATTER/CONTROLLER

# Table 8.2 Flag Options

|                          | Flag                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | h : Head load flag                                   | When $h = 1$ : The head is loaded at the beginning of the command execution. When $h = 0$ : The head is loaded when the verify operation starts if the V flag is "1". It is not loaded if the V flag is "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Type 1 commands          | V : Verify flag                                      | When V =1: The contents of the track register are compared with the ID track address after head positioning. The seek error status bit is set if the desired track address is not found by the time the diskette has gone through 6 rotations.  When V =0: The track verification is not performed.                                                                                                                                                                                                                                                                                                                                                                        |

|                          | r <sub>1</sub> , r <sub>0</sub> : Stepping rate flag | The stepping rate is determined by the value of these 2 bits as well as by the CLK frequency and TEST input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                          | u : Update flag                                      | When $u=1$ : The track register is updated with each step pulse: It is incremented (or decremented) by 1 for each step-in (or step-out) pulse. When $u=0$ : Track register is not updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Type 2/Type3<br>Commands | E : 15ms delay flag(at 2MHz clock)                   | When E =1: Sampling of the head load timing input starts with the 15ms delay after the head load output has been set to "1". An advance is made to the next step when HDLD·HLDT = "1" is established.  When E =0: Sampling of the head load timing input starts immediately after the head load output has been set to "1". An advance is made to the next step when HDLD·HLDT = "1" is established.  The "next step" is the TG43 output update.                                                                                                                                                                                                                           |

|                          | m : Multi-sector read/write flag                     | When m =1: Multi-sector read/write is performed. Upon completion of one sector read/write, the sector register value is incremented by 1, the next sector is sought and read/write is performed again. Upon completion of the final sector read/write operation, the next sector is not found even when sought and so at the sixth rotation of the diskette the RNF error bit is set and the operation is concluded. This command can also be concluded with the Type 4 command.  When m =0: Read/write for single sector is performed.                                                                                                                                    |

| Type 2<br>commands       | S : Side select flag                                 | When S =1: "1" is compared with the ID side number when the C flag is "1".  When S =0: "0" is compared with the ID side number when the C flag is "1".  No comparison is performed when C =0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                          | C : Side compare flag                                | When C =1: The S flag and ID side number are compared. When C =0: The ID side number is not compared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                          | a <sub>0</sub> : Data address mark flag              | When $a_0 = 1$ : The deleted data mark "F8" (hexadecimal) is written into the data field address mark.  When $a_0 = 0$ : The data mark "FB" (hexadecimal)-is written into the data field address mark.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Type 4<br>command        | I : Interrupt condition flag                         | When $l_0=1$ : The interrupt request output is set to "H" at the ready input rising edge. When $l_1=1$ : The interrupt request output is set to "H" at the ready input falling edge. When $l_2=1$ : The interrupt request output is set to "H" with the index pulse input. When $l_3=1$ : The command being executed is terminated and the interrupt request output is set to "H" immediately. When $l_0=l_1=l_2=l_3=0$ : No interrupt request is generated but the command being executed is terminated. This command is executed so that the interrupt request output, which has been set by the Type 4 command, is reset by the following command write or status read. |

## $oldsymbol{\circ}$

# 9. ELECTRICAL CHARACTERISTICS

# 9.1 ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                            | Conditions                      | Limits         | Unit |

|------------------|--------------------------------------|---------------------------------|----------------|------|

| Vcc              | Supply voltage                       |                                 | −0.5~7         | ٧    |

| Vı               | Input voltage                        | With respect to V <sub>SS</sub> | −0.5~7         | ٧    |

| Vo               | Output voltage                       |                                 | -0.5~7         | ٧    |

| Pd               | Power dissipation                    | Ta=25℃                          | 350            | mW   |

| Topr             | Operating free-air temperature range |                                 | 0~70           | °C   |

| T <sub>stg</sub> | Storage temperature range            |                                 | <b>−65∼150</b> | °C   |

# 9.2 RECOMMENDED OPERATING CONDITIONS ( $T_a=0\sim70^{\circ}C$ , unless otherwise noted)

| Combal          | D                        |                      | Unit |       |      |

|-----------------|--------------------------|----------------------|------|-------|------|

| Symbol          | Parameter                | Min                  | Nom  | Max   | Unit |

| V <sub>CC</sub> | Supply voltage           | 4. 75                | 5    | 5. 25 | V    |

| V <sub>SS</sub> | Supply voltage           |                      | 0    |       | V    |

| V <sub>IH</sub> | High-level input voltage | 2                    |      |       | V    |

| VIL             | Low-level input voltage  | V <sub>ss</sub> -0.5 |      | 0.8   | V    |

# 9.3 ELECTRICAL CHARACTERISTICS (Ta=0~70°C, Vcc=5V±5%, unless otherwise noted)

| Symbol          | D                                               | Total condition                     |      | Limits |     |      |

|-----------------|-------------------------------------------------|-------------------------------------|------|--------|-----|------|

|                 | Parameter                                       | Test condition                      | Min  | Тур    | Max | Unit |

| V <sub>OH</sub> | High-level output voltage                       | $I_{OH} = -200 \mu A$               | 2.4  |        |     | ٧    |

| VoL             | Low-level output voltage                        | I <sub>OL</sub> =1.8mA              |      |        | 0.4 | ٧    |

| Icc             | Supply current                                  |                                     |      |        | 70  | mA   |

| <b>!</b> 1      | Input current.(HDLT, TEST, WF/VFOE, WPRT, DDEN) | V₁=V <sub>CC</sub> ~0V              | -100 |        | 10  | μΑ   |

|                 | Input current other inputs                      | V <sub>I</sub> =V <sub>CC</sub> ~0V | -10  |        | 10  | μA   |

| loz             | Off-state output current                        | V <sub>I</sub> =V <sub>CC</sub> ~0V | -10  |        | 10  | μA   |

# FLOPPY DISK FORMATTER/CONTROLLER

# TIMING REQUIREMENTS ( $\tau_a=0\sim70^{\circ}$ , $\nu_{cc}=5v\pm5\%$ , $\nu_{ss}=0v$ , unlese otherwise noted)

| 0                                             |                                                 | Alternative      | T 4   141            |      |         |       |      |

|-----------------------------------------------|-------------------------------------------------|------------------|----------------------|------|---------|-------|------|

| Symbol                                        | Parameter                                       | symbol           | Test conditions      | Min  | Тур     | Max   | Unit |

| t <sub>SU(A-R)</sub><br>t <sub>SU(CS-R)</sub> | Address setup time before read and chip select  | TSET             |                      | 50   |         |       | ns   |

| th(R-A)<br>th(R-CS)                           | Address hold time after read and chip select    | THLD             |                      | 10   |         |       | ns   |

| t <sub>W(R)</sub>                             | Read pulse width                                | TRE              | C <sub>L</sub> =50pF | 280  |         |       | ns   |

| t <sub>SU(A-W)</sub><br>t <sub>SU(CS-W)</sub> | Address setup time before write and chip select | TSET             |                      | 50   |         |       | ns   |

| th(W-A)                                       | Address hold time after write and chip select   | THLD             |                      | 10   |         |       | ns   |

| t <sub>w(w)</sub>                             | Write pulse width                               | TWE              |                      | 200  |         |       | ns   |

| tsu(DQ-W)                                     | Data setup time before write                    | TDS              |                      | 250  |         |       | ns   |

| th(w-DQ)                                      | Data hold time after write                      | TDH              |                      | . 20 |         |       | ns   |

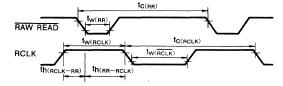

| t <sub>W(RR)</sub>                            | Raw read pulse width                            | T <sub>PW</sub>  | (Note1. 2)           | 100  |         | 250   | ns   |

| t <sub>C(RR)</sub>                            | Raw read cycle time                             | Tbc              | (Note 3)             | 1600 | 2000    |       | ns   |

| t <sub>W(RCLK)</sub>                          | Read clock high-level width                     | Ta               | (Note 4)             | 800  |         |       | ns   |

| tw(RCLK)                                      | Read clock low-level width                      | Tb               | (Note 4)             | 800  | 1       |       | ns   |

| t <sub>C(RCLK)</sub>                          | Read clock cycle time                           | T <sub>C</sub>   |                      | 1600 |         |       | ns   |

| th(RCLK-RR)                                   | Read clock hold time before raw read            | T <sub>X1</sub>  |                      | 40   |         |       | ns   |

| 4.                                            |                                                 |                  | FM                   | 40   |         |       | ns   |

| th(RR-RCLK)                                   | Read clock hold time after raw read             | T <sub>X2</sub>  | MFM                  | 40   |         |       | ns   |

|                                               | West- data and a middle                         | <b>-</b>         | FM                   | 450  | 500     | 550   | ns   |

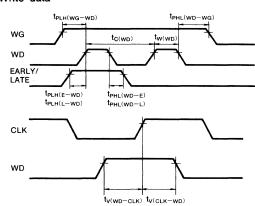

| t <sub>W(WD)</sub>                            | Write data pulse width                          | Twp              | MFM                  | 150  | 200     | 250   | ns   |

| t <sub>C(WD)</sub>                            | Write data cycle time                           | Tbc              |                      |      | 2, 3, 4 |       | μs   |

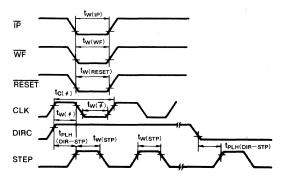

| t <sub>W(≠)</sub>                             | Clock high-level pulse width                    | TCD <sub>1</sub> |                      | 230  | 250     | 20000 | ns   |

| t <sub>W(\$\delta\$)</sub>                    | Clock low-level pulse width                     | TCD <sub>2</sub> |                      | 200  | 250     | 20000 | ns   |

| tw(RESET)                                     | Reset pulse width                               | TMR              |                      | 50   |         |       | μs   |

| t <sub>W(IP)</sub>                            | Index pulse width                               | TIP              | (Note 5)             | 10   |         |       | μs   |

| t <sub>W(WF)</sub>                            | Write fault pulse width                         | TWF              | (Note 5)             | 10   |         |       | μs   |

# SWITCHING CHARACTERISTICS (Ta=0~70°C, V<sub>CC</sub>=5V±5%, V<sub>SS</sub>=0V, unless otherwise noted)

| Sumb of                                          | Parameter                                         | Alternative      | <b>-</b>             |      |     |     |      |

|--------------------------------------------------|---------------------------------------------------|------------------|----------------------|------|-----|-----|------|

| Symbol                                           | Farameter                                         | symbol           | Test conditions      | Min  | Тур | Max | Unit |

| •                                                | Deposition time from write note to write date     | _                | FM (Note 5)          |      | 2   |     | μs   |

| t <sub>PLH</sub> (wg-wd)                         | Propagation time from write gate to write data    | Twg              | MFM (Note 5)         |      | 1   |     | μs   |

| t <sub>PLH(E-WD)</sub><br>t <sub>PLH(L-WD)</sub> | Propagation time from early or late to write data | Ts               | MFM (Note 5)         | 125  |     |     | ns   |

| t <sub>PHL(WD-E)</sub>                           | Propagation time from write data to early or late | Th               | MFM (Note 5)         | 125  |     |     | ns   |

|                                                  | Propagation time from write data to write gate    | Twt              | FM (Note 5)          |      | 2   |     | μs   |

| t <sub>PHL</sub> (WD-WG)                         |                                                   |                  | MFM (Note 5)         |      | 1   |     | μs   |

| t <sub>PZV(R-DQ)</sub>                           | Output enable time after read                     | TDACC            | C <sub>L</sub> =50pF |      | ,   | 250 | ns   |

| t <sub>PVZ(R-DQ)</sub>                           | Output disable time after read                    | TDOH             | C <sub>L</sub> =50pF | 50   |     | 150 | ns   |

| t <sub>PHL(R-DRQ)</sub>                          | Propagation time from read to DRQ                 | TDRR(RD)         |                      |      |     | 250 | ns   |

| t <sub>PHL(R-INTRQ)</sub>                        | Propagation time from read to INTRQ               | TIRR(RD)         | (Note 5)             |      |     | 500 | ns   |

| t <sub>PHL(W-DRQ)</sub>                          | Propagation time from write to DRQ                | TDRR(WR)         |                      |      |     | 250 | ns   |

| t <sub>PHL(W-INTRQ)</sub>                        | Propagation time from write to INTRQ              | TIRR(WR)         | (Note 5)             |      |     | 500 | ns   |

| t <sub>W(STP)</sub>                              | Step pulse width                                  | TSTP             | (Note 5)             | 2or4 |     |     | μs   |

| t <sub>PLH(DIR-STP)</sub>                        | Propagation time from direction to step           | TDIR             | (Note 5)             | 12   |     |     | μs   |

|                                                  | Mulha dahailid kima bafasa alast.                 | <b>+</b> .       | CLK=1MHz MFM         | 200  |     |     | ns   |

| t <sub>V(WD-CLK)</sub>                           | Write data valid time before clock                | Twdi             | CLK=2MHz MFM         | 30   |     |     | ns   |

|                                                  | Marian alaka walial kima aska walani.             | <b>+</b> .       | CLK=1MHz MFM         | 50   |     |     | ns   |

| t <sub>V(CLK-WD)</sub>                           | Write data valid time after clock                 | Twd <sub>2</sub> | CLK=2MHz MFM         | 50   |     |     | ns   |

Note 1: The pulse of RAW READ may be any width if pulse is entirely within RCLK. When the pulse occurs in the RCLK window, RAW READ pulse width must be less than 300 ns for MFM mode and 600 ns for FM mode at CLK=2MHz. Times double for 1MHz.

2: 100 ns pulse width is recommended for the RAW READ pulse in 8 MFM mode.

RAW READ cycle time  $T_{C(RR)}$  and WD cycle time  $T_{C(WD)}$  is normally  $2\mu s$  in MFM and  $4\mu s$  in FM. Times double when CLK=1MHz. The polarity of RCLK during RAW READ is not important. Times double when CLK=1MHz.

# 9.6 TIMING DIAGRAM

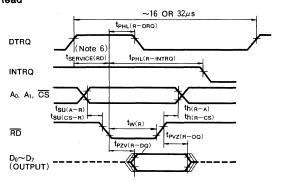

#### Read

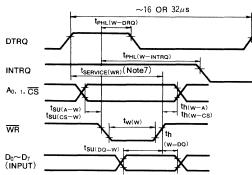

#### Write

FLOPPY DISK FORMATTER/CONTROLLER

Note 6:  $t_{SERVICE(RD)}$  maximum value, FM: 27.5 $\mu$ s, MFM: 13.5 $\mu$ s 7:  $t_{SERVICE(WR)}$  maximum value; FM: 23.5 $\mu$ s, MFM: 11.5 $\mu$ s

### Input data

### Write data

#### Others

### 10. OTHERS

Refer to the description of M5W1791-02P for further information.